### VOICE OF THE ENGINEER

Oct **13** Issue 21/2005 www.edn.com Research Update: news on GaN FETs, fuel cells, and more Pg 30

Global Designer: Handsets gain traction; automotive software goes horizontal Pg 32

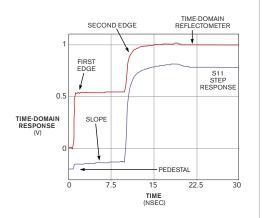

Howard Johnson sees beyond the edge Pg 36

Design Ideas Pg 99

## NAND versus NOR

WHICH FLASH IS BEST FOR BOOTIN' YOUR NEXT SYSTEM? PAGE 41

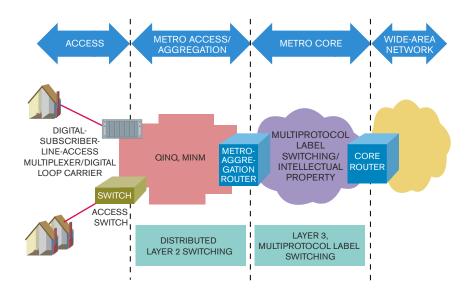

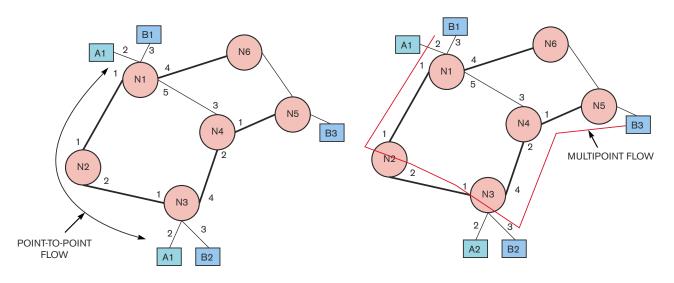

### OPTIMIZED LEARNING IN METRO SWITCHES

ETHERNET EXTENDS INTO AGGREGATION AND CORE NETWORKS PAGE 69

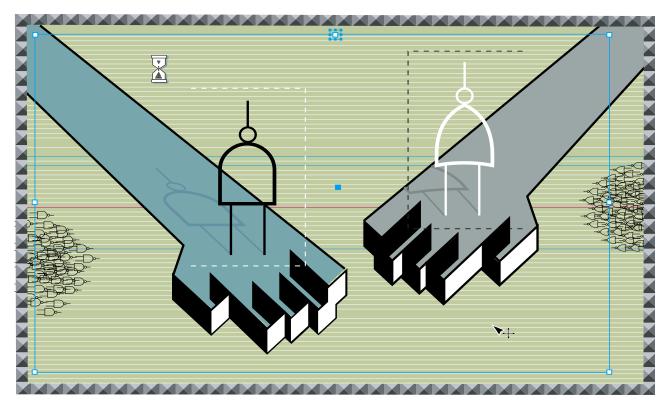

## INSTIGATING A PLATFORM IUG OF WAR:

GRAPHICS VENDORS HUNGER FOR CPU SUPPLIERS' TURF PAGE 50

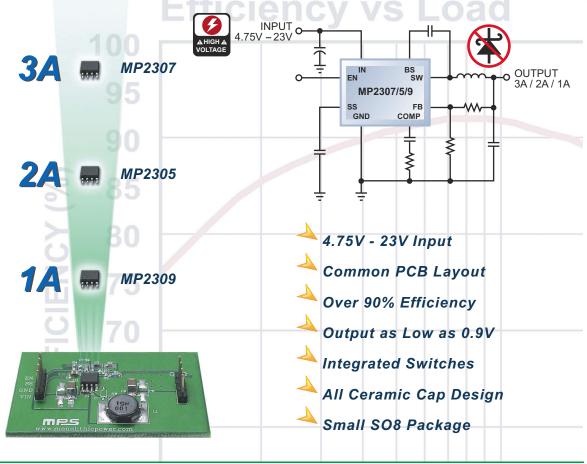

> INTERLEAVING DC/DC CONVERTERS BOOST EFFICIENCY AND VOLTAGE PAGE 77

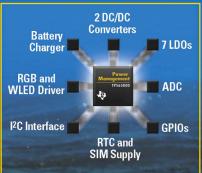

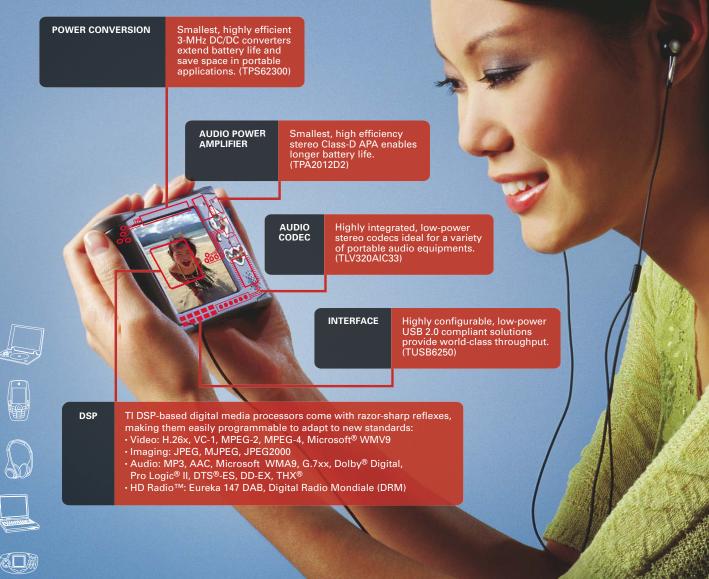

## **One Chip, One Solution** Integrated Handheld Power Management

The TPS65800 power management IC extends battery life in portable designs while occupying up to 70% less board space than discrete solutions. Designed for multimedia and communication devices powered by a 1-cell lithium-ion battery, the TPS65800 integrates complete battery management, highly efficient power conversion, including a white LED driver, and an I<sup>2</sup>C control interface in an 8 x 8 mm<sup>2</sup> QFN package.

#### Save Up to 70% Board Space

High Performance. Analog. Texas Instruments.

For a datasheet, sample and evaluation module, visit www.ti.com/tps65800

Technology for Innovators<sup>™</sup>

Technology for Innovators and the red/black banner are trademarks of Texas Instruments. 1224A0 © 20

1.800.344.4539 · www.digikey.com

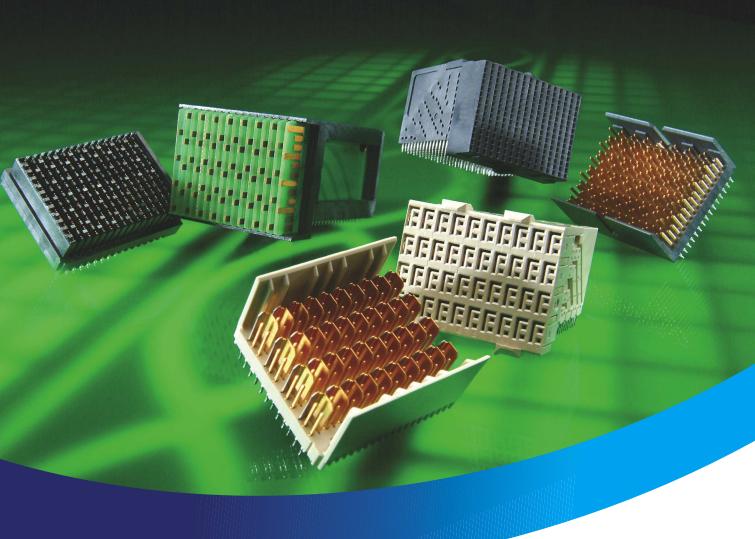

## At Tyco Electronics, we have more ways to bring you up to speed.

Getting the high speed performance you need is one thing. Achieving it at the cost you had in mind is quite another. That's why, at Tyco Electronics, we offer more options when it comes to interconnect solutions. Our depth of products allows us to not only meet your precise cost and performance requirements of today, but also help you migrate towards your designs of tomorrow. We even offer extensive simulation and modeling tools that help ensure you get the performance to meet your needs. And with so many options, there's definitely one thing we don't offer: a bias. For more information visit **www.tycoelectronics.com/productinfo** and request our high-speed connector catalog.

North America 800-522-6752 • Europe +49 6251 1330 • Asia +81-44-844-8292 • www.tycoelectronics.com MULTIGIG RT, Z-PACK and TYCO are trademarks Our MultiGig RT connector is specified per standards set by VITA-41 and VITA-46.

The Z-PACK HM-Zd connector is specified by PICMG<sup>®</sup> consortium as Advanced TCA<sup>®</sup> standard for Zone 2 Advanced Differential Fabric connector.

Our Z-PACK MAX high performance back plane connector systems are designed for cost pressured, high density applications.

## **Next Generation Power Modules** Pb-free and 50% Smaller

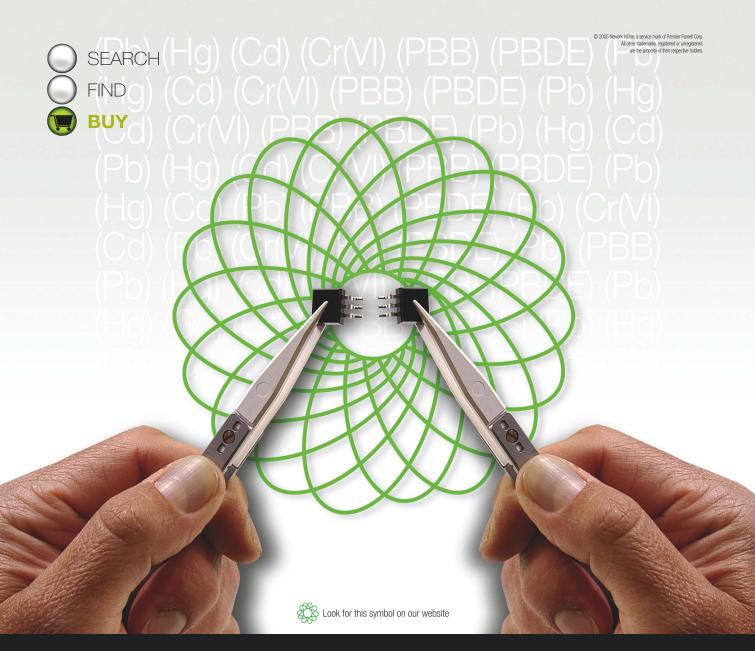

The new **PTN78 series** is the next generation of TI's popular PT78 series wide-input wide-output general purpose power module – it's 50% smaller, higher performance and more cost effective. Designed to be Pb-free, RoHS compatible and high-temperature solder process capable, the new PTN78 series also includes adjustable output voltage and on/off inhibit. Choose either positive or negative output voltage. The best just got better!

| Device      | V <sub>IN</sub> (V) | I <sub>OUT</sub> | V <sub>OUT</sub> (V) |

|-------------|---------------------|------------------|----------------------|

| PTN78000W/H | 7 to 36             | 1.5A             | 2.5 to 12.6/12 to 22 |

| PTN78060W/H | 7 to 36             | ЗA               | 2.5 to 12.6/12 to 22 |

| PTN78020W/H | 7 to 36             | 6A               | 2.5 to 12.6/12 to 22 |

| PTN78000A   | 7 to 29             | 1.5A             | −3 to −15            |

| PTN78060A   | 9 to 29             | ЗA               | −3 to −15            |

| PTN78020A   | 9 to 29             | 6A               | –3 to –15            |

#### NEW!

**Power Management Selection Guide** Data Sheets, Samples, Plug-in Power Selector Guide

www.ti.com/ptn78000 ° 800.477.8924, ext. 2355

Technology for Innovators<sup>™</sup>

#### ► Applications

- Industrial controls, HVAC systems

- Test and measurement

- Medical instrumentation

- AC/DC adaptors

- Vehicular, marine and avionic electronics

#### ► Features

- High efficiency

- Wide input voltage range 7-36V

- Adjustable output voltage

- On/off inhibit

- Current limit/over-temp shutdown

- Operating temp

-40°C to 85°C

- Pb-free

Texas Instruments

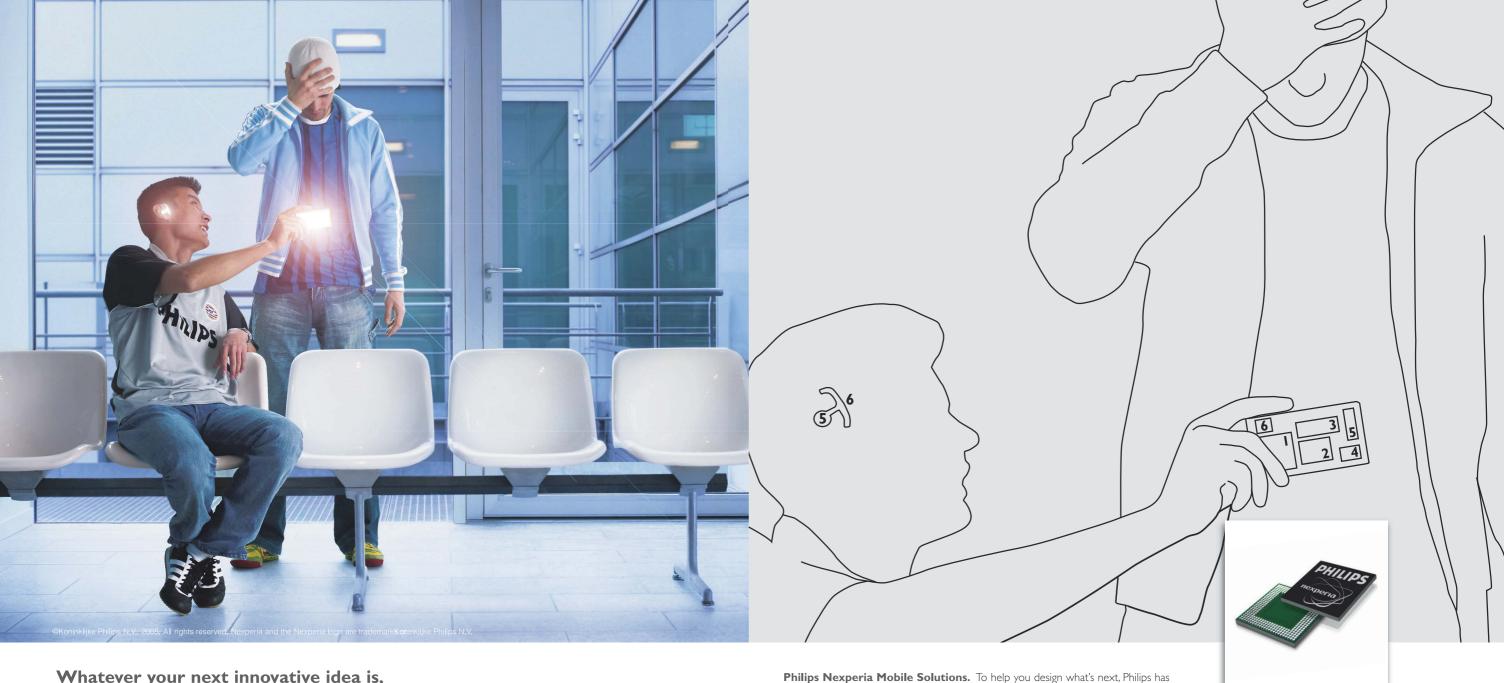

#### Whatever your next innovative idea is, we'll help you design it.

Philips Nexperia Mobile Solutions. A mobile phone that can buy tickets to the game. A mobile phone that allows you to watch the game when you can't get to the stadium. A mobile phone that takes a picture of your friend coming to terms with his team's loss and shares it with your other friends. People buy their mobile phones today expecting much more than just a mobile phone. That's why you need an adaptable technology solution that can be tailored and changed as fast as your consumer needs. With Philips Nexperia Mobile Solutions, you'll find flexibility in platform design to customize your handset offering for different features and markets, and a total system approach that enables easy porting of various software applications. We address every type of GSM/GPRS/EDGE/UMTS/TD-SCDMA mobile

phone, and provide expertise in value-added features such as connectivity, security, broadcast and multimedia. So no matter what's next in mobile phones, Philips will help you design it.

complete handset reference designs incorporating the following functions:

- **I. Display** Complete display sub-assemblies and LifePix<sup>™</sup> enhancement algorithms bring multimedia content to life.

- 2. Cellular All the core system elements, including proven Nexperia baseband, power management, RF, PA, and software protocol stack.

- 3. Multimedia Advanced Nexperia processors, and partnerships with software suppliers for exciting audio/video/gaming features.

- 4. Broadcast DVB-H for TV-on-Mobile broadcasts, and the smallest FM radios in the industry.

- 5. Connectivity Bluetooth and WiFi coexistence solutions, and NFC for easy network setup, and mobile ticketing and payment.

- 6. Speaker Excellent quality speakers and microphones enhance the audio/visual experience.

www.philips.com/nm

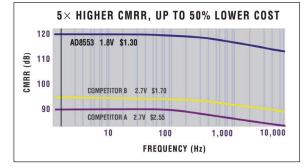

## The first 1.8 V auto-zero instrumentation amp. Best-in-class performance for the lowest price.

#### AD8553 Performance...

- High CMRR: 120 dB min

- Low offset drift: 0.1 μV/°C max

- Low offset: 25 μV max

- Low noise: 0.7 μV p-p (0.01 Hz to 10 Hz)

- Pb-free package: 10-lead MSOP

- Price: \$1.30/1k quantities

#### ...where it matters

- Pressure sensors

- Strain gages

- · Medical instrumentation

#### Precision and value for low voltage designs

If you're designing medical or industrial systems, our new AD8553 combines all the in-amp features you wanted for portable applications. *Extended battery life*—with operation from 5.5 V down to 1.8 V and a shutdown mode that reduces total supply current to less than 4 µA, the AD8553 is the most battery-friendly in-amp in the industry. *Excellent signal conditioning*—high CMRR, low offset voltage, low drift,

and low noise combine to make the AD8553 ideal for precision applications. **Design simplicity**—forget using discrete solutions that require laser trimming and more board space, or in-amps that require an external op amp to drive the  $V_{REF}$  pin. **Lowest cost**—In addition to better performance and power savings, the AD8553 costs 30% to 50% less than the competition. You can't build or buy better in-amp performance and value for your next low voltage design. To learn more, please visit our website.

#### www.analog.com/autozero-inamp

THE LEADER IN HIGH PERFORMANCE ANALOG

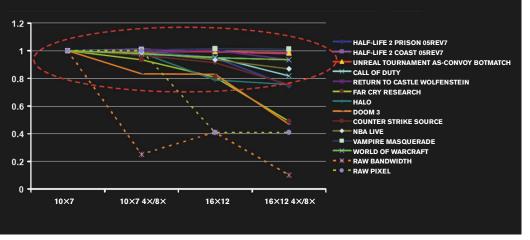

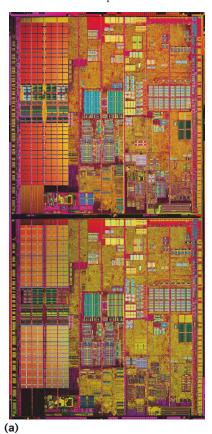

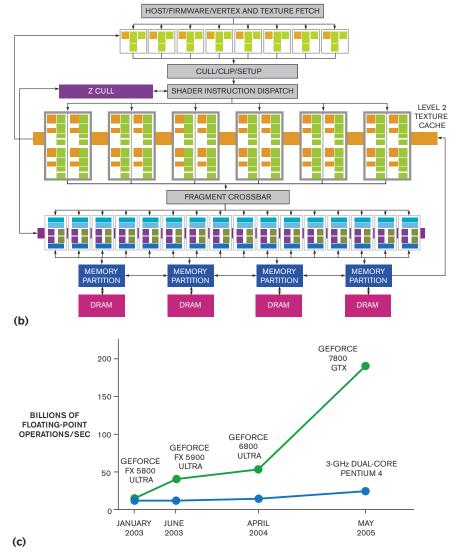

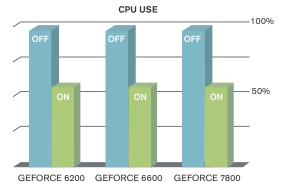

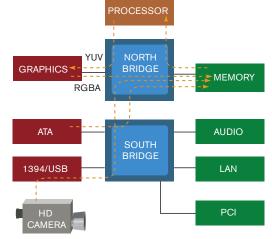

#### Instigating a platform tug of war: Graphics vendors hunger for CPU suppliers' turf

50 Processor vendors' fiscal fortunes hinge on the ability to sell increasingly powerful chips. Graphics-processor vendors, too, depend on upgrades to pave a path to continued success. These upgrades will increasingly rely on stealing functions that the CPU once handled. by Brian Dipert, Senior Technical Editor

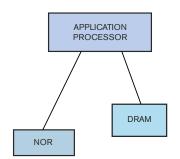

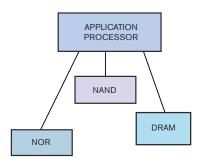

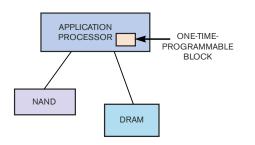

#### NAND versus NOR

Which flash is best for bootin' your next system? by Michael Santarini, Senior Editor

## Optimized learning in metro switches

Ethernet extends into aggregation and core networks.

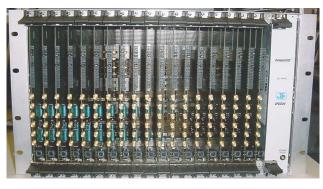

by Gopal Garg, Cypress Semiconductor, and R Thirumurthy, Midas Communication Technologies

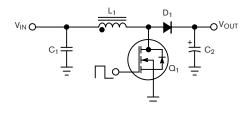

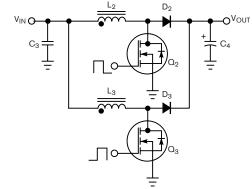

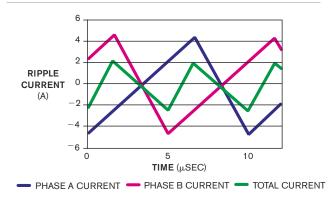

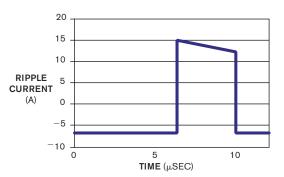

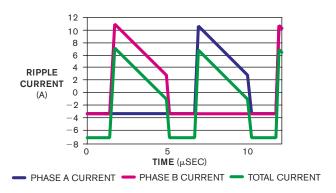

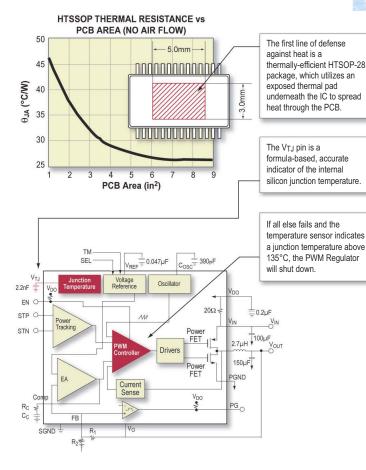

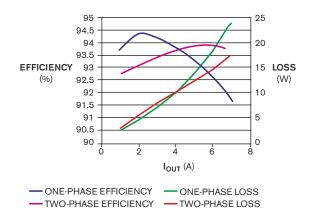

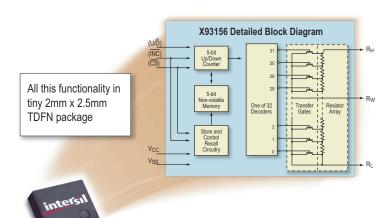

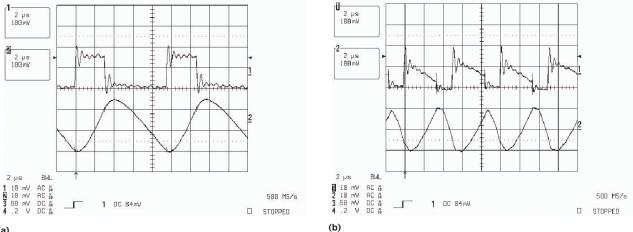

#### Interleaving dc/dc converters boost efficiency and voltage

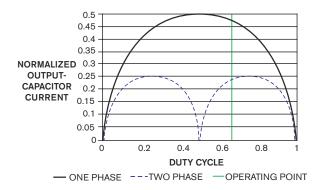

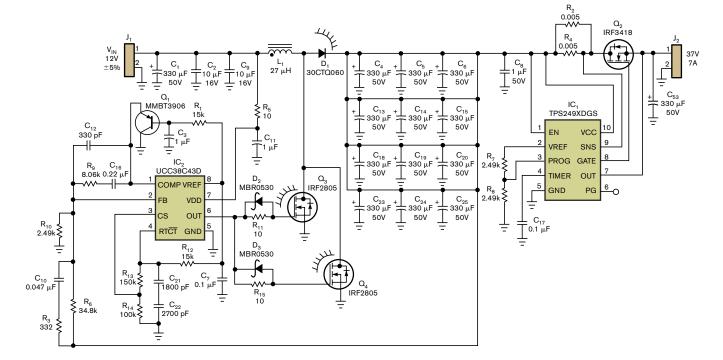

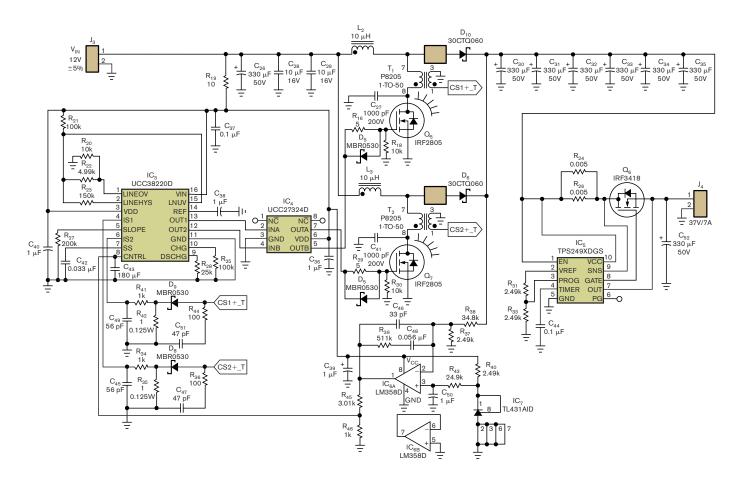

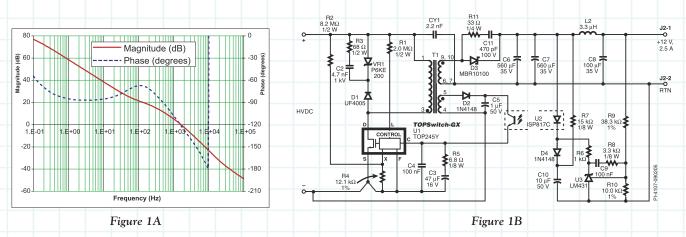

Though somewhat more complex than singlephase designs, interleaved-boost converters run cooler, occupy less space, and can cost less. by John Betten and Robert Kollman, Texas Instruments

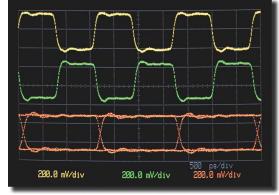

#### The secrets of successful communications using LVDS

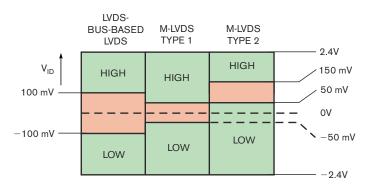

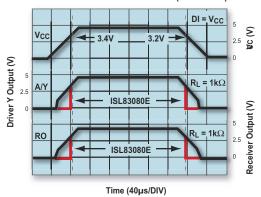

89 Reliable single- and mixed-technology LVDS designs require attention to voltage levels, noise margins, and drive levels. by Jim Dietz and Richard Hubbard, Texas Instruments

## DESIGNIDEAS

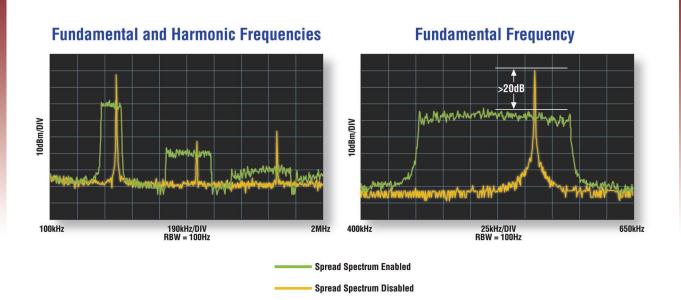

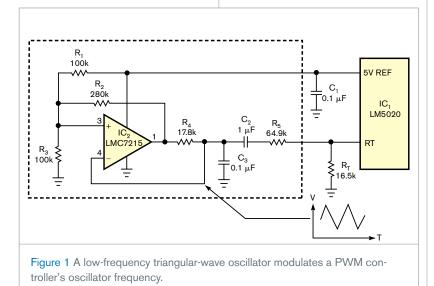

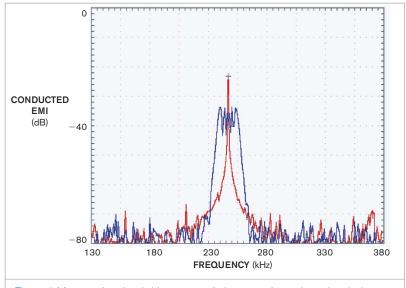

Dither a power converter's operating frequency to reduce peak emissions

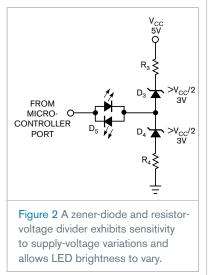

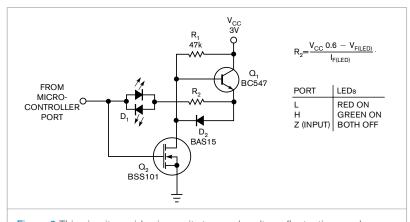

100 Single-port pin drives dual LED

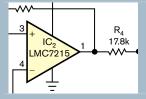

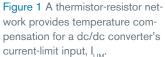

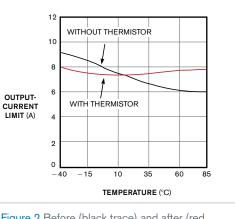

102 Network linearizes dc/dc converter's current-limit characteristics

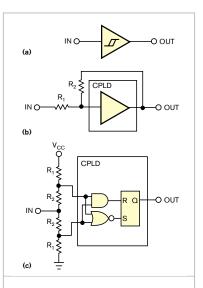

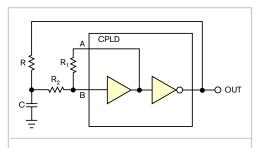

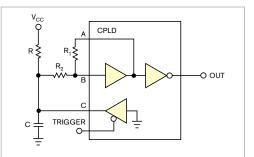

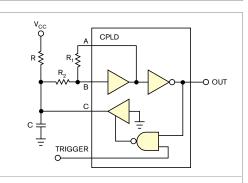

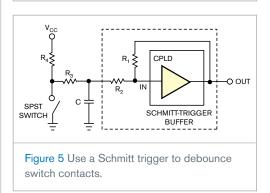

104 Add a Schmitt-trigger function to CPLDs, FPGAs, and applications

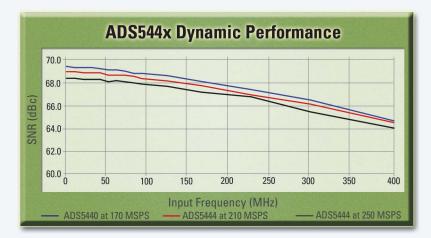

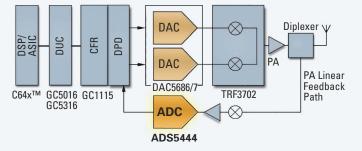

## High Speed, Top Performance! 13-Bit, 250-MSPS ADC

Sample Application: Wideband, High IF DPD Feedback Receiver

The new **ADS5444** from Texas Instruments sets a new benchmark for high-speed ADCs, providing best-in-class performance at 250 MHz. Look to TI for a complete portfolio of high-speed ADCs, including the recently announced ADS5440 13-bit, 250 MSPS ADC.

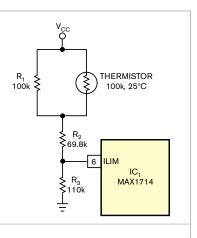

| Device  | Resolution<br>(Bits) | Speed<br>(MSPS) | SNR<br>(dBc)       | SFDR<br>(dBc)    |

|---------|----------------------|-----------------|--------------------|------------------|

| ADS5444 | 13                   | 250             | 68 at 230 MHz IF   | 75 at 230 MHz IF |

| ADS5440 | 13                   | 210             | 68 at 230 MHz IF   | 79 at 230 MHz IF |

| ADS5500 | 14                   | 125             | 69.5 at 100 MHz IF | 82 at 100 MHz IF |

| ADS5424 | 14                   | 105             | 74 at 50 MHz IF    | 93 at 50 MHz IF  |

| ADS5541 | 14                   | 105             | 71 at 100 MHz IF   | 86 at 100 MHz IF |

| ADS5423 | 14                   | 80              | 74 at 50 MHz IF    | 94 at 50 MHz IF  |

| ADS5520 | 12                   | 125             | 68.7 at 100 MHz IF | 82 at 100 MHz IF |

| ADS5521 | 12                   | 105             | 69 at 100 MHz IF   | 86 at 100 MHz IF |

#### Applications

- Software-defined radio

- Base stations:

- Wideband receiver

- High IF receiver

- PA linearization

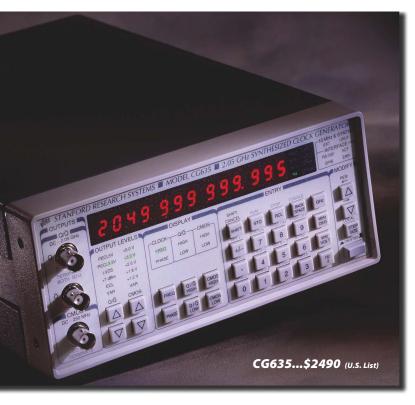

- Instrumentation

- Test and Measurement

#### Features

- 100 MHz IF: SNR = 68.7 dBc;

SFDR = 73 dBc

- 230 MHz IF: SNR = 68 dBc; SFDR = 75 dBc

- Fully buffered analog inputs

- 2.2 Vpp differential input voltage

- 3.3 V LVDS compatible outputs

- TQFP-80 PowerPAD™ package

- Industrial temperature range –40°C to +85°C

- Price: \$95 1k

New!

V Texas Instruments

Amplifier and Data Converter Selection Guide, Datasheets, Samples, Evaluation Modules

#### www.ti.com/ads5444 ° 800.477.8924, ext. 2695 -

Technology for Innovators

## contents 10.13.05

- 23 Embedded modem eases datacommunications woes

- 23 Get your wall power ac/dc or ac/ac

- 23 RF connector links boards, uses no cable

- 24 Desktop platform supports voice over WiFi

- 24 Line terminator says "hasta la vista" to reflections

- 26 Processor integrates more peripheral support

- 26 EPIC computer pushes temperature extremes

- 28 SMT plasma arrester features low, stable capacitance

- 28 Package provides IDE for heterogeneous distributed systems

- 30 **Research Update:** Coating may dispel condensation fog; GaN FET produces 174W at 6 GHz; Microstrip line uses layered dielectrics for front-side antenna patch; Fuel cell beats power-density benchmarks

- 32 Global Designer: Low-cost handsets gain traction in India; Japanese-automotive software goes horizontal

## DEPARTMENTS & COLUMNS

- 14 **EDN.comment:** Industry rocks the night away

- 36 Howard Johnson: See beyond the edge

- 38 Tales from the Cube: Coping with changes of employment

- 122 Reality Check: Cell phones shrink, their market explodes

## PRODUCT ROUNDUP

- 108 Discrete Semiconductors: Rad-hard MOSFETs, silicon-controlled rectifiers, low-leakage Schottky diodes, and more

- 110 Embedded Systems: Stand-alone radios, development-tool suites, PMC cards, and more

- 112 Microprocessors: Low-power-consumption microcomputers, evaluation kits, IPsec software, and more

EDN @ (ISSN#0012-7515), (GST#123397457, R.B.I. Intl Pub Mail #0280844) is published biweekly, 26 times per year, by Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Reed Business Information, a division of Reed Elsevier Inc, is located at 360 Park Avenue South, New York, NY 10010. Jim Casella, Chief Executive Officer; Stephen Moylan, President, Boston Division. Periodicals postage paid at Littleton, CO 80129-2345. Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Telephene Moylan, President, Boston Division. Periodicals postage paid at Littleton, CO 80129-2345. Telephene Moylan, President, Boston Division. Periodicals postage paid at Littleton, CO 80129-2345. Telephene (303) 470-4445. POSTMASTER: Send address changes to EDN %, PO Box 7500. Highlands Ranch, CO 80163-7500. EDN © copyright 2005 by Reed Elsevier Inc. Rates for nonqualified subscriptions, including all issues: US, \$149.90 one year; Canada, \$205.90 one year, (anda, \$205.90 one year; Canada, \$205.90 one year. Except for special issues where price changes are indicated, single copies are available for \$10.00 US and \$15.00 foreign. Publications Mail Agreement No. 40685520. Return undeliverable Canadian addresses to: Deutsche Post, 4960-2 Walker Road, Windsor ON N9A 6U3. E-mail: subsmail@reedbusiness.com. Please address all subscriptions mail to EDN %, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. EDN @ is a registered trademark of Reed Elsevier Properties Inc, used under licenses. A Reed Business Information Publication/Volume 50, Number 21 (Pinted in USA)

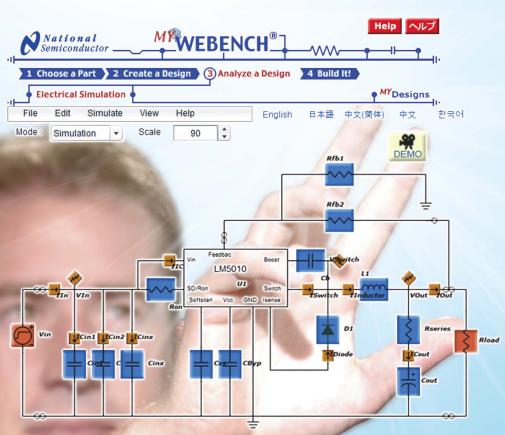

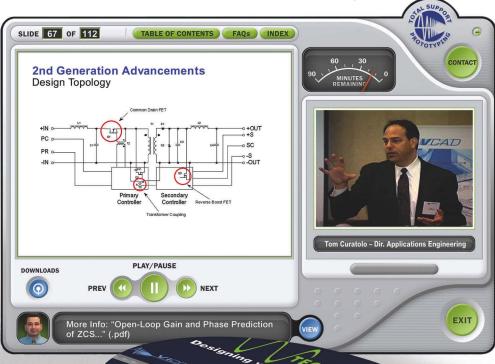

# Design Today, Prototype Tomorrow

Superior Design Tools and Resources for the Analog Designer

#### WEBENCH® Online Tools

Get to market faster by accelerating your design process. WEBENCH® tools allow you to select products, design, and receive a custom prototype kit in 24 hours. webench.national.com

#### **Application Solutions**

Over 100 interactive system block diagrams with a list of recommended parts for: automotive, broadcast video, data communications, displays, industrial, medical, and consumer applications. solutions.national.com

#### 24/7 Online Seminars

View over 50 on-demand design focused seminars for power, amplifiers, audio, data acquisition, interface, and thermal management.

www.national.com/onlineseminar

#### **Analog University®**

Get your design right the first time. Log on to Analog University for fast, free information from the pros at National, including in-depth design courses. analogU.national.com

# EDN online contents

#### **ONLINE ONLY**

Check out these online-exclusive articles:

Opinion: DFM alliance depends on EDA cooperation By Michael Santarini, Senior Editor

Don't be surprised if the design-for-manufacturability effort, though noble, takes more time than projected.

→ www.edn.com/article/CA6260497

#### Bluetooth SIG offers qualification "cookbook"

The online and downloadable tools aim to make the certification of new products a step-by-step affair.

→ www.edn.com/article/CA6260461

### More mind-boggling math: Adding and subtracting unsigned BCD

Clive "Max" Maxfield continues his series on binary-coded-decimal math.

→ www.edn.com/article/CA6258681

#### Meeting the demands of video on demand

As consumers in greater numbers adopt video-on-demand services, cable operators must make sure their networks can rise to the occasion.

www.edn.com/article/CA6256544

### INNOVATION AWARDS: CALL FOR NOMINATIONS

We're now accepting nominations for the 16th annual *EDN* Innovation Awards. Learn how to nominate your company's products and engineers using our easy online process. Nominations close November 23, after which *EDN*'s readers will pick the winners. We'll hand out the awards in early April 2006.

→ www.edn.com/innovation

### VOIP chip enables multimedia-rich cordless phones

Broadcom's new chip aims to imbue WiFibased cordless telephones for home use with features such as video streaming.

www.edn.com/article/CA6258645

### Single-board Pentium M computer targets military use

SBS Technologies says its new 3U CompactPCI-based single-board computer tolerates harsh environments and offers low voltage and low heat.

→ www.edn.com/article/CA6258204

#### Opinion: When RFI overwhelms RKE

By Bill Schweber, Executive Editor

With wireless systems, engineers must keep in mind that the transmission path they are counting on resides in a crowded swamp. → www.edn.com/article/CA6252229

#### Compression tool shrinks design files by 20×

SoftJin's file-compression program allows users to transfer ever-growing GDSII IC layout files more quickly.

#### | BRIAN'S BRAIN

Is the Xbox a curse for graphics-chip companies? Is Apple's iPod nano a killer of minia-

ture hard disks? Are consumers ready for networkattached storage? Are graphics companies taking a page from PT Barnum (relying on suckers to make a buck)? The answers (or at least opinions) are in Brian's Brain, a blog by *EDN* Senior Technical Editor Brian Dipert. This week, Brian's Brain also contains a raft of information supplementing Brian's graphics-chip cover story in this issue.

→ www.edn.com/briansbrain

#### **FROM THE VAULT**

Articles and extras from the EDN archives that relate to this issue's contents.

#### Related to ...

NAND versus NOR (pg 41):

#### Hitting their stride

Nonvolatile-memory upstarts draw near established leaders. → www.edn.com/article/CA495735

www.eun.com/article/CA49370

#### Flash forward to the future

The global digital-consumer trend signals a potential changing of the guard in the flash-memory industry.

→ www.edn.com/article/CA474720

See beyond the edge (pg 36):

#### VNAs and TDRs

Taking the measure of the new millennium. → www.edn.com/article/CA633462

Signal-integrity modeling of gigabit backplanes, cables, and connectors using TDR

→ www.edn.com/article/CA231568

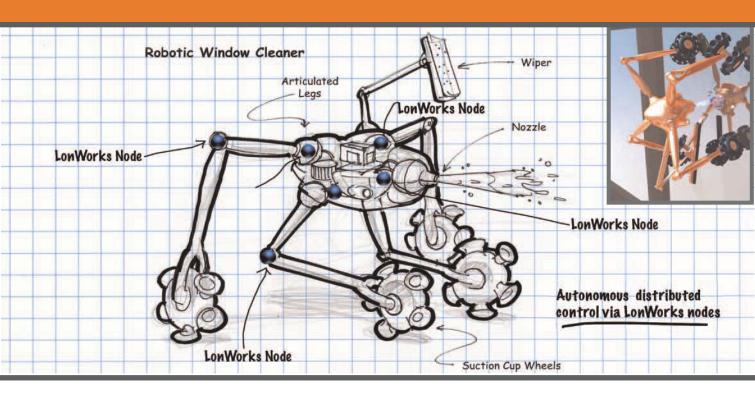

# DESIGN WITHOUT LIMITS

What you design is your business. Adding distributed control throughout your application is ours. Our LONWORKS® platform is a worldwide standard for networking anything you want to control—pumps, motors, valves, fans—even a remote-controlled window washer. Add networking features to your products and watch them deliver more than you thought possible. Start today with our NodeBuilder® development tool, or ease into your LONWORKS development with our new Mini EVK. Call +1 408-938-5200 Ito earn more about our development tools, or visit us online at www.echelon.com/embedded.

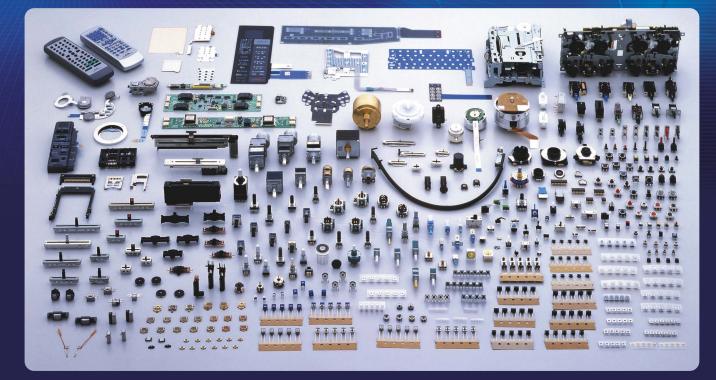

### Innovation driven by a commitment to excellence.

$(\mathbf{R})$

Striving to create, nurture and accumulate the highest quality electronic components, ALPS continues to forge ahead in an ever-changing marketplace just like we have for over fifty years.

Visit our Web site for more details: http://www.alps.com

ALPS ELECTRIC (USA), INC. http://www.alpsusa.com 910 E. Hamilton Avenue Suite #500 Campbell, CA 95008, U.S.A. Phone +1(408)361-6400 Fax +1(408)226-7301 HEAD OFFICE http://www.alps.co.jp 1-7, Yukigaya-otsuka-cho, Ota-ku, Tokyo, Japan, 145-8501 Phone. +81(3)3726-1211 Fax. +81(3)3728-1741

EDN.COMMENT

#### BY JOHN DODGE, EDITOR IN CHIEF

## Industry rocks the night away

usic has long been a release for many working in the high-pressure electronics and IT industries. In the '80s, Borland founder Philippe Kahn held jams at the once-huge, now-defunct Comdex computer conference (Link 1). The music was so-so, but anyone could play, showing that people working 60 hours a week did have lives. The music is better at the Demo conference, where innovators get to show off new products and ideas to a crowd of influencers and investors (Link 2). Long-time *Wall Street Journal* high-tech reporter Don Clark always makes Neil Young proud at this gathering of high tech's glitterati. One year, Shawn Colvin showed up.

The electronics industry now has dozens if not hundreds of bands and musicians to call its own. One noteworthy troupe is Full Disclosure, whose members include rivals from Cadence and Synopsys, along with Gartner Dataquest analyst Gary Smith, who tracks the EDA industry. Full Disclosure plays rhythm and blues and is in its glory every year at DAC.

Another electronics-industry band,

The electronics industry now has dozens if not hundreds of bands and musicians to call its own.

Spurious Freedom, aspires to play fundraisers for charities. Formed in 2003, Spurious Freedom takes its name from "spurious-free dynamic range"—a key specification in ADCs. Fame may not be the band's forte, but it hasn't entirely managed to avoid the spotlight. Spurious Freedom was scheduled to compete Oct 7 and 8 at the Rock and Roll Hall of Fame's annual Battle of the Corporate Bands in Cleveland after winning a regional contest in Los Angeles on July 9. The band specializes in '70s and '80s rock tunes.

The band's first show celebrated 100 days of success regarding a bone-marrow transplant for bass guitarist Shawn Eubanks' daughter, who is battling leukemia. These six middle-aged minstrels and one sound engineer hail—or hailed—from Texas Instruments' Analog Division. All engineers, they include guitarist Michael Lanz, vocalist Thomas Armendarez, keyboardist Michael Ashton, drummer Tony Zizzo, rhythm guitarist Lon Mitchell, sound engineer Lenard Milholland, and guitarist Eubanks.

The electronics industry has lately been no stranger to good causes. Another example is a joint campaign by Xilinx, Linear Technologies, and Summit Microelectronics to become a "Colon Cancer Free Zone." The trio is collaborating with the American Cancer Society to encourage coloncancer screening. And now we have the tragic destruction of the Gulf Coast and New Orleans. I'd love to hear what the electronics industry is doing to help victims in those areas. Write me at john.dodge@reedbusiness.com.EDN

#### WEB LINKS

http://news.com.com/Perspective +A+last+hurrah+for+Comdex/2010-1069\_3-965975.html.

www.demo.com/demo2/.

#### MORE AT EDN.COM

To listen to Spurious Freedom, go to www.edn.com/051013ed1.

# The proof is empirica More than 30,000 RF engineers use Agilent EEsof EDA

Eagleware-Elanix is now part of Agilent EEsof EDA.

#### www.agilent.com/find/eesof-innovations

There's truth in numbers. Agilent EEsof EDA is the top design software choice among engineers for the vast the majority of the world's wireless devices.

The fact is derived from software products with undisputed breadth of functionality. Agilent EEsof EDA applications were created for RF engineers by RF engineers. They have the capabilities you need the most. And now with the addition of Eagleware-Elanix you have further ease of use, new synthesis technology, and additional pricing options other products can't touch. Agilent's team of EDA experts releases multiple improvement updates each year. And Agilent has the largest number of technology partners, application examples, and technical articles in the industry.

Work the proof yourself. Agilent EEsof EDA can be customized to fit the precise needs of your projects and budget. Visit www.agilent.com/find/eesof-innovations to find out more.

### Agilent Technologies

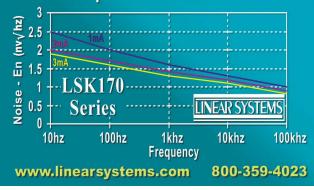

## **1nV Low Noise JFET**

LSK170

LSK170

Low Noise <1nV Low Capacitance, 20pf **High Input Impedance Selected Idss Grades** Available in SOT23 Package Pin for Pin Replacement for 2SK170

PRESIDENT, BOSTON DIVISION/ PUBLISHING DIRECTOR. EDN WORLDWIDE Stephen Moylan, 1-781-734-8431; fax: 1-781-

290-3431; smoylan@reedbusiness.com EDITOR IN CHIEF

John Dodge, 1-781-734-8437; fax: 1-781-290-3437; john.dodge@reedbusiness.com EDITOR AT LARGE

Maury Wright, 1-858-748-6785 mgwright@edn.com

EXECUTIVE EDITOR Bill Schweber, 1-781-734-8447; fax: 1-781-290-3447; bschweber@edn.com

MANAGING EDITOR Kasey Clark, 1-781-734-8436; fax: 1-781-290-3436; kase@reedbusiness.com

EXECUTIVE EDITOR, ONLINE Matthew Miller, 1-781-734-8446; fax: 1-781-290-3446: mdmiller@reedbusiness.com

SENIOR ART DIRECTOR Mike O'Leary, 1-781-734-8307; fax: 1-781-290-3307; moleary@reedbusiness.com

EMBEDDED SYSTEMS Warren Webb, Technical Editor 1-858-513-3713; fax: 1-858-486-3646 wwebb@edn.com

ANALOG/COMMUNICATIONS, DISCRETE SEMICONDUCTORS Joshua Israelsohn, Technical Editor 1-781-734-8441; fax: 1-781-290-3441 jisraelsohn@edn.com

EDA. MEMORY. PROGRAMMABLE LOGIC Michael Santarini, Senior Editor 1-408-345-4424 michael.santarini@reedbusiness.com

MICROPROCESSORS, DSPs, TOOLS Robert Cravotta, Technical Editor 1-661-296-5096; fax: 1-781-734-8070 rcravotta@edn.com

MASS STORAGE, MULTIMEDIA, PERIPHERALS, AND PC-CORE LOGIC Brian Dipert, Senior Technical Editor; 1-916-760-0159; fax: 1-781-734-8070; bdipert@edn.com

POWER SOURCES, ONLINE INITIATIVES Margery Conner, Technical Editor; 1-805-461-8242; fax: 1-805-461-9640 mconner@connerbase.com

> DESIGN IDEAS EDITOR Brad Thompson

edndesignideas@reedbusiness.com SENIOR ASSOCIATE EDITOR

Frances T Granville, 1-781-734-8439 fax: 1-781-290-3439; f.granville@reedbusiness.com

ASSOCIATE EDITOR Maura Hadro Butler, 1-908-928-1403; mbutler@reedbusiness.com

WEB/CPS PRODUCTION COORDINATOR Contact for contributed technical articles Heather Wiggins, 1-781-734-8448; fax: 1-718-290-3448; hwiggins@reedbusiness.com

EDITORIAL AND ART PRODUCTION Diane Malone, Manager; 1-781-734-8445 fax: 1-781-290-3445 Steve Mahoney, Production Editor 1-781-734 8442; fax: 1-781-290-3442

Adam Odoardi, Prepress Manage 1-781-734-8325; fax: 1-781-290-3325 NEWS EDITOR

Jeff Berman, 1-781-734-8449; fax: 1-781-290-3449; jeff.berman@reedbusiness.com

CONTRIBUTING TECHNICAL EDITOR Dan Strassbera, strassberaedn@att.net

EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000; fax: 1-781-734-8070. Address changes or subscription inquiries: phone 1-800-446-6551; fax: 1-303-470-4280; subsmail@reedbusiness.com. For a free subscription, go to www.getfreemag.com/edn. Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Include your mailing label.

#### COLUMNISTS

Ron Mancini: Howard Johnson, PhD: Bonnie Baker

PRODUCTION Dorothy Buchholz, Group Production Director 1-781-734-8329

Kelly Brashears, Production Manager 1-781-734-8328; fax: 1-781-734-8086 Linda Lepordo, Production Manager

1-781-734-8332; fax: 1-781-734-8086 Pam Boord, Advertising Art

1-781-734-8313 fax 1-781-290-3313 EDN EUROPE Graham Prophet, Editor, Reed Publishing

The Quadrant, Sutton, Surrey SM2 5AS +44 118 935 1650; fax: +44 118 935 1670; gprophet@reedbusiness.com

EDN ASIA Raymond Wong, Managing Director/ Publishing Director raymond.wong@rbi-asia.com Kirtimaya Varma, Editor in Chief kirti.varma@rbi-asia.com

EDN CHINA William Zhang, Publisher and Editorial Director wmzhana@ida-rbi.com.cn John Mu. Executive Editor iohnmu@ida-rbi.com.cn

EDN JAPAN Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Kenji Tsuda, Editorial Director and Editor in Chief tsuda@reedbusiness in Takatsuna Mamoto, Deputy Editor in Chief t.mamoto@reedbusiness.ip

The EDN Editorial Advisory Board serves as an industry touchstone for the editors of EDN worldwide, helping to identify key trends and voicing the concerns of the engineering community.

> DENNIS BROPHY Director of Business Development Mentor Graphics

DANIS CARTER Principal Engineer, Tyco Healthcare

CHARLES CLARK

Technical Fellow, The Boeing Company DMITRII LOUKIANOV

System Architect, Intel RON MANCINI

Staff Scientist, Texas Instruments GABRIEL PATULEA

Design Engineer, Cisco MIHIR RAVEL

VP Technology, National Instruments DAVE ROBERTSON

Product Line Director, Analog Devices SCOTT SMYERS

VP Network and System Architecture Division, Sonv

TOM SZOLYGA Program Manager, Hewlett-Packard JIM WILLIAMS

Staff Scientist, Linear Technology

# ANALOG edge

### **Featured Products**

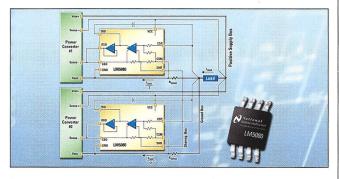

#### **Modular Current Sharing Controller**

The LM5080 is a simple and cost-effective load-share controller that provides all of the functions required to balance the currents delivered from multiple power converters operated in parallel. The LM5080 implements an average program method of active load share control which adjusts the output voltage of individual power stages either up or down to deliver nearly equal currents to a common load. The average program method improves stability and reduces the output voltage tolerance when compared to other common load sharing methods. The LM5080 supports two common applications for load share controllers: external control in which the load share circuit balances currents between separate power modules (bricks), and internal control where the load share circuit is integrated into the voltage regulation loop of each power converter module or circuit.

#### Features

- Single-wire star link current share bus

- No precision external resistors necessary

- 3V to 15V bias voltage range

- Adaptable for high or low side current sensing

- Flexible architecture allows 4 modes of operation:

- Negative remote sense adjustment

- Positive remote sense adjustment

- Trim or reference adjustment

- Feedback divider adjustment

The LM5080 is available in MSOP-8 packaging and is ideal for use in consumer electronics, industrial test equipment, data communications systems, automotive power systems, distributed power systems, and battery-powered applications.

#### www.national.com/pf/LM/LM5080.html

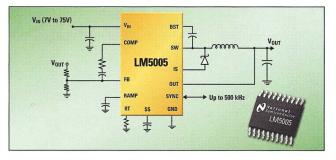

## DESIGN *idea:* Simplified Power Supply Design

#### First 7V to 75V Input, 2.5A Buck Regulator

The LM5005 high-voltage switching regulator features all of the functions necessary to implement an efficient high-voltage buck regulator using a minimum of external components. This easy-to-use regulator includes a 75V N-Channel buck switch with an output current capability of 2.5A. The regulator control method is based upon current-mode control utilizing an emulated current ramp. Current-mode control provides inherent line feed-forward, cycle-by-cycle current limiting, and ease of loop compensation. The use of an emulated control ramp reduces noise sensitivity of the pulse-width modulation circuit, allowing reliable control of very small duty cycles necessary in high input voltage applications. The operating frequency is programmable from 50 kHz to 500 kHz.

#### Features

- Integrated 75V power MOSFET supports load currents up to 2.5A

- Adjustable output voltage from 1.225V

- Unique, easy-to-use emulated peak current mode control topology enables high frequency operation at V<sub>IN</sub> up to 75V

- Programmable switching frequency with bi-directional synchronization capability simplifies system design

- Highly integrated, high-speed, full-feature PWM regulator reduces overall solution size

The LM5005 is available in a power enhanced TSSOP-20 package featuring an exposed die attach pad to aid thermal dissipation. It is ideal for use in consumer electronics, telecommunications, data communications systems, automotive power systems, and distributed power applications.

#### www.national.com/pf/LM/LM5005.html

#### edge.national.com

## **DESIGN** *idea*

### PWM DC-DC Controllers with Built-In Start-Up Regulators Simplify Switching Power Supply Design

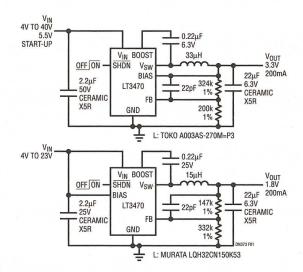

Ithough PWM DC-DC switching power converters are based on simple topologies, making practical power supplies out of them requires the addition of various functions such as start-up bias, soft-start, switch driving, regulation, short circuit protection, over-voltage protection, over-temperature protection, etc. Today, most of these functions are usually implemented within a compact DC-DC PWM controller integrated circuit.

However, the problem of starting the DC-DC converter in telecom and other high-voltage applications (i.e., where the input voltage exceeds about 15V) is often not addressed. The controller requires a bias supply voltage to run from so that it can produce gate drive pulses and other required signals. But at turn-on the only voltage available is the input voltage, which, if it is greater than 15V, is typically too high to be used as the bias and gate drive supply voltage. It is therefore necessary to lower the

input voltage to 15V or below to startup the power supply. Once the supply is running, the output voltage or a voltage off of a transformer or inductor winding can be used to provide the bias supply for the IC.

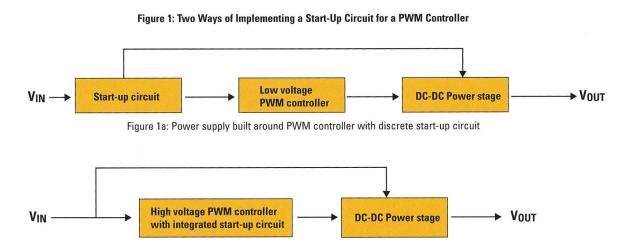

But most DC-DC controllers are designed without start-up circuitry, and the power supply designer is expected to add a separate start-up circuit and a bias supply to them (*Figure 1a*). This improves the versatility of the PWM controllers, allowing them to be operated with a wider input voltage range, but the extra start-up circuitry they require increases in the complexity and size of the power supply.

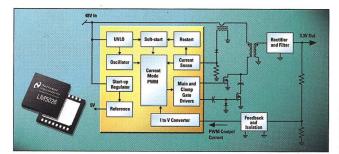

National has solved this problem for the designer in its LM50xx family of 8V to 100V PWM controllers (which includes the LM5020, LM5025, LM5030, and others) by integrating a high-voltage start-up circuit within the IC (*Figure 1b*). This is achieved by fabricating the controller using a 100V process.

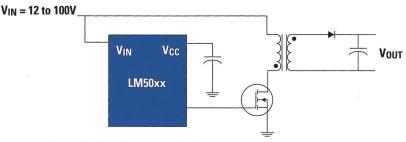

The high-input voltage can then be directly applied to the V<sub>IN</sub> pin of the controller, which is the input to an internal linear voltage regulator. This regulator produces a voltage V<sub>CC</sub> of about 8V that is used to provide start-up power to the controller. The V<sub>CC</sub> voltage of the linear regulator is made externally accessible at the V<sub>CC</sub> pin, for several reasons.

One reason is that the  $V_{CC}$  pin is the connection point in the linear regulator for an external output capacitor that keeps the  $V_{CC}$  voltage clean.

Another reason is that  $V_{CC}$  can serve as the power source for other low-voltage ICs in the circuit such as op amps, logic, and gate drivers.

The  $V_{CC}$  pin can also be used to reduce the power dissipation in the controller and to increase the efficiency of the power supply. LM50xx controllers will operate indefinitely off of the input voltage and the internally generated  $V_{CC}$

Figure 1b: Power supply built around PWM controller with integrated start-up circuit

#### edge.national.com

voltage (as illustrated in *Figure 2a* in a flyback converter). But this leads to increased power dissipation in the IC. This dissipation is

$$PD = (V_{IN} - V_{CC})I_S$$

where  $I_S$ , the supply current of the controller is the sum of the controller quiescent current, and  $I_G$ , the frequencydependent gate drive current. This MOSFET current is given by

$$_{G}=0_{FS}f_{S}$$

where  $Q_{GS}$  is the total gate charge of the MOSFET at a gate voltage of  $V_{CC}$  and  $f_S$  is the switching frequency.

$P_D$  can be excessively large for the controller at high-input voltages, high-switching frequency, and when the IC is driving a large MOSFET that requires a significant gate-drive current.

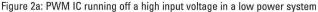

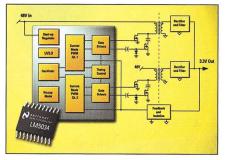

LM50xx controllers are designed such that this power dissipation can be circumvented. In all switching power supply topologies, it is easy to derive a bias voltage from a transformer or inductor winding once the power supply has started running. In LM50xx controllers, this voltage (once available), can be applied directly to the V<sub>CC</sub> pin to provide power for the IC, and can also be used to power other parts of the system. In all LM50xx controllers, if this applied voltage is greater than the 8V output of the internal regulator, the regulator shuts down, eliminating the power dissipation just described. This can lead to an efficiency improvement of 1% or more if the bias supply is properly designed. (Figure 2b)

Nevertheless, in lower power systems with lower input voltages it is often advantageous to dispense with the bias supply and to run the supply off of the internal linear regulator. This simplifies the supply and reduces its cost and is often used with LM50xx controllers for output power levels of up to about 30W. Figure 2: Three Ways of Powering the LM50xx Family of PWM Controllers

Figure 2b: PWM IC running off a bias supply in a high-power system

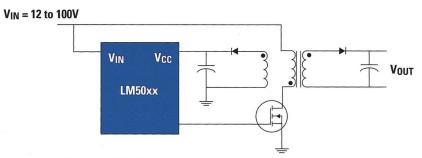

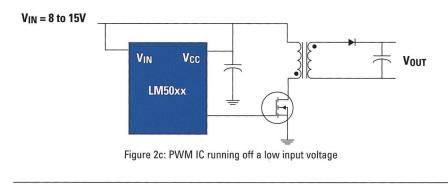

If the input voltage lies between 8 and 15V, the LM50xx controllers are particularly easy to power. The  $V_{IN}$  and  $V_{CC}$  pins can simply be tied together and to the input voltage, which then directly powers the controller. (*Figure 2c*). If the voltage exceeds 15V the two pins cannot be tied together, and the input voltage has to be higher than about 12V in order for the controller to start up.

In summary, National Semiconductor's high-voltage PWM controllers with integrated start-up regulators allow the power supply designer to reduce circuit complexity, solution size, component costs, design time, and to increase circuit reliability.

Visit <u>edge.national.com</u> for the online Analog Edge technical journal and an archive of design ideas, application briefs, and other informative links.

#### National Semiconductor The Sight & Sound of Information

#### edge.national.com

### **Featured Products**

## Current-Mode Controller for Forward Converters with Active-Clamp Reset

The LM5026 PWM controller contains all of the features necessary to implement power converters utilizing the active clamp/reset technique with current-mode control. With the active-clamp technique, higher efficiencies and greater power densities can be realized compared with conventional catch winding or RDC clamp/ reset techniques. The device can be configured to control either a P-Channel or N-Channel clamp switch. The main gate driver features a compound configuration, consisting of both MOS and Bipolar devices, providing superior gate drive characteristics. Additional features include line under-voltage lockout, cycle-bycycle current limit, PWM slope compensation, soft-start, 1 MHz capable oscillator with synchronization input/output capability, precision reference, and thermal shutdown.

#### Features

- Wide range (8V to 100V) start-up bias regulator

- Two high-speed power MOSFET drivers: 3A main output driver and 1A clamp driver

- User-programmable maximum duty-cycle and UVLO hysteresis thresholds

- User-programmable gate driver overlap and dead-time

- Versatile dual-mode over-current protection with hiccup mode delay timer

The LM5026 is available in TSSOP-16 or thermally enhanced LLP-16 packaging and is ideal for use in telecommunications power systems, +42V automotive power systems, -48V distributed power systems, industrial power supplies, and multi-output power supplies.

#### www.national.com/pf/LM/LM5026.html

#### Industry's First 100V Dual Interleaved Active Clamp Current-Mode Controllers

The LM5032 and LM5034 are flexible controllers that can be configured to control either two independently regulated outputs or a single, high-current output from two

primary power stages. In the first case, the two PWM channels operate 180 degrees out of phase with one another, or are interleaved, which reduces the input ripple current. In the single-output configuration, the interleaving also reduces ripple current in the output filter capacitor. The LM5032 controller can be used for designing dual-interleaved boost, flyback or standard forward converters. The LM5034 controller is specifically designed for interleaved forward converters with active clamp transformer reset.

#### Features

- Two independent current-mode controllers

- Interleaved single or dual output operation

- Compound 2.5A main FET gate drivers

- Active clamp FET gate drivers

- Integrated 100V start-up regulator

- Up to 1 MHz switching frequency programmed by a single resistor

- Programmable maximum duty cycle

- Adjustable soft-start and input undervoltage sensing

- Adjustable deadtime between main and active clamp gate drivers

The LM5032/34 are available in TSSOP-16 (LM5032) and TSSOP-20 (LM5034) packaging and are ideal for use in telecom infrastructure, networking, industrial, and automotive power supplies.

#### www.national.com/pf/LM/LM5032.html www.national.com/pf/LM/LM5034.html

© National Semiconductor Corporation, 2005. National Semiconductor, 🔗, and LLP are registered trademarks and Analog Edge is a service mark of National Semiconductor Corporation All other brand or product names are trademarks or registered trademarks of their respective holders. EVERYONE

11

10

GET

IN

11

SYNCH.

In unison, in step. Share critical information more securely. Combine multiple file types into a single, searchable document. View and respond to project feedback seamlessly. And get everyone on the same page. Acrobat 70. Try it for free at adobe.com/collaborate and see how much more your team can do. Better by Adobe:

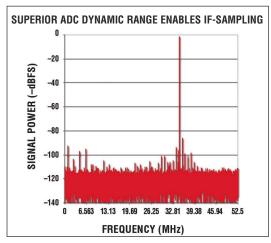

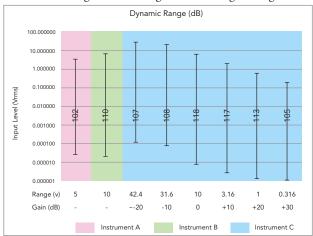

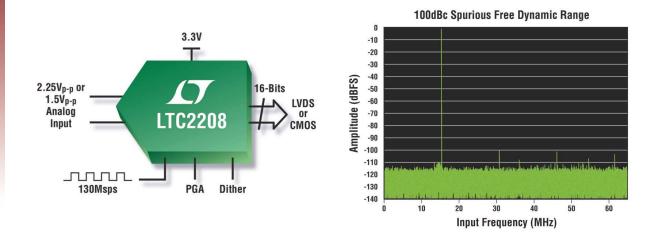

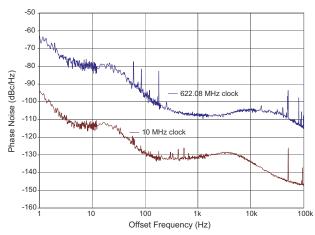

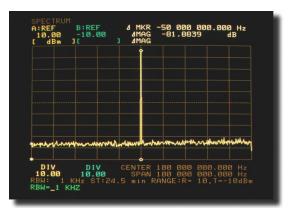

## Specifying A/D Converters: Considerations for IF-Sampling Applications

Choosing the ADC with the highest resolution or sampling speed is often not enough to satisfy the performance demands presented by IF-sampling architectures. ADCs for IF-sampling applications must support high input frequencies while also maintaining adequate SNR, SFDR, and SINAD performance. These features enable designers to eliminate one or more mixing stages and simplify filtering, thereby reducing cost and helping to meet endsystem objectives.

Wideband signals having complex modulation—such as those used in many wireless communications, instrumentation, and radar systems—can exhibit time-varying bursts and transients. Furthermore, the data carried by these signals is often spread over multiple channels.

The ADC for these types of architectures must have sufficient input bandwidth to adequately capture and digitize this data. The ADC's dynamic range must also be high enough to detect small signals in the presence of blockers or other large signals in the bandwidth of interest.

#### **Dynamic Range and Noise Requirements**

In wideband CDMA systems having a base data rate of 3.84 MHz, data converter clock rates of  $16\times$ ,  $20\times$ ,  $24\times$ , and  $32\times$  are viable. A data converter running at 92.16 MSPS provides good noise performance, and 16-bit ADCs that sample at 100 MSPS are available today. If lower sampling rates are used, the SNR required increases by 1 dB for 76.8 MSPS and 2 dB for 61.44 MSPS.

32k point single-tone FFT/ADC: 105 MSPS, 70.3 MHz A<sub>IN</sub>

The receiver conversion gain and noise figure (NF) sets the ADC's required SNR. At the antenna, the noise spectral density is -174 dBm/Hz, or that of thermal noise. For a conversion gain of 40 dB and a noise figure of 3 dB, the noise spectral density (NSD) at the ADC input will be -131 dBm/Hz (-174 + 40 + 3). If the ADC noise floor is 10 dB below that of the front end noise, it will contribute about 0.1 dB to the overall NF of the receiver. Therefore, a maximum ADC noise floor of -141 dBm/Hz is desirable.

For IF-sampling applications, the total noise of the ADC can be determined by simple integration. For example, a 10 MHz bandwidth signal would have total noise of -71 dBm. This is calculated by adding the effect of the 10 MHz bandwidth [10 log (10 MHz) = 70 dB] to the 1 Hz noise floor of -141 dBm. If the full scale range of the ADC is 4 dBm, the required minimum full-scale SNR for the ADC is then 75 dB.

#### Selecting the Optimum A/D Converter

What types of ADCs meet the needs of IF-sampling architectures? Typically, they require ADCs with 14 bits to 16 bits of resolution that deliver superior SNR at high input frequencies. Advances in high speed ADC technology offer improved SNR, low additive jitter, higher sampling rates, and increased input frequency capability. These features enable engineers to design more efficient base stations, radar, and measurement equipment.

Additionally, the instrumentation used to validate communications systems must meet even tighter specifications, so as not to mask or distort the end-product's actual performance. These systems allow designers to accurately characterize signals of interest with minimum added distortion from the data converter. The AD9446 16-bit, 100 MSPS ADC from Analog Devices is an example of wideband converter technology that is targeted for IF-sampling applications in communications instrumentation. With a 70 MHz analog input and 100 MSPS sampling rate, the AD9446 provides a spurious-free dynamic range of 83 dB; it provides 82 dB of SFDR with a 100 MHz analog input. For more information on the AD9446 and other data converters for IF-sampling applications, please visit *www.analog.com/PerformanceADCs.* ▶

Author Profile: **Joanne Mistler** is a marketing engineer with Analog Devices' High Speed Converter Group in Wilmington, MA. She has 22 years of RF/MW experience, focusing on low noise synthesizer design, digital communications, and test and measurement applications.

# EDITED BY FRAN GRANVILLE EDITED BY FRAN GRANVILLE INNOVATIONS & INNOVATORS

## Embedded modem eases data-communications woes

argeting applications in remote-monitoring systems, point-of-sale terminals, home-security networks, medical devices, and backup-communication systems, Radicom Research recently announced a low-power, low-cost modem. Standard AT commands control the Half-Inch Modem, which measures just  $1 \times 1 \times 0.3$  in. with a -40 to  $+85^{\circ}$ C operating temperature. The modem includes a built-in data pump, modem controller, and onboard international DAA (data-access arrangement). With power consumption as low as 18 mA in sleep mode, the modem delivers data rates as high as 56 kbps. Alex Tsau, vice president of operations at Radicom,

The new Half-Inch Modem from Radicom Research offers drop-in data communications for embedded-system designs.

says, "The Half-Inch Modem simplifies the design process for data-communications functions, allowing designers to add connectivity to their applications in a very small space."

The self-contained modem requires only a serial TTL interface and phone-line access to provide data, fax, and voice operation. Handset-interrupt and connection-detection features allow the modem to share a phone line with other equipment, eliminating the cost of a dedicated line. The Half-Inch Modem is available now, and prices begin at \$21 (1000).

−by Warren Webb **Radicom Research Inc**, www.radi.com.

#### Get your wall power ac/dc or ac/ac

The ubiquitous wall wart usually provides low-voltage, isolated dc output from the ac mains, but some applications need low-voltage ac, either for circuit operation or because the device it supplies will perform its own local or multivoltage regulation. A new series of Class 2 plug-in units from Foster Transformer provides outputs ranging from 9 to 24V ac, depending on model. The ULlisted transformers are rated for 10 to 50 VA; prices for a basic 10-VA model start at \$3.10 (1000).-by Bill Schweber **Foster Transformer.** www.foster-transformer.com.

### RF connector links boards, uses no cable

Getting dc power or digital signals from one board to an adjacent one is a challenge, but getting RF signals to make the leap is even more difficult. A compression coaxial connector from Tyco Electronics can make the task easier. The Blindmate board-to-board connector has one side that you solder onto the base pc board, and the other side mates by pressing against a tin- or gold-plated target pad on the adjacent target board, using internal spring pressure. Using the one-piece connector is far simpler than using cable-based interfaces or two separate board connectors with a spacer wedged between them.

The connector provides a  $50\Omega$  path and operates to 6 GHz with return loss of at least 20 dB to speeds as high as 2.1 GHz. Tyco offers models for 6.65-, 10-, and 14-mm board spacing, and the connector tolerates both axial (interboard) and radial misalignments:  $\pm 1$  mm for the axial misalignment for the 10- and 14-mm versions and  $\pm 0.3$  mm for the shortest version. The tolerance for radial misalignment is  $\pm 0.8$  mm for all three versions. The Blindmate connector sells for \$5.80 (10,000).—by Bill Schweber

>Tyco Electronics, www.tycoelectronics.com.

Making an RF path between parallel boards is simpler when you eliminate a cable assembly and instead use a spring-loaded compression connector; the Tyco Blindmate operates as fast as 6 GHz and comes in three lengths.

## pulse

### Desktop platform supports voice over WiFi

zimuth Systems' twomodule W-Series desktop WiFi (wireless-fidelity)-test platform enables software designers to test station roaming, performance, function, and range. The system comes in a portable, three-slot chassis and includes a custombuilt STM-501 module. According to an Azimuth spokesman, the STM-501 is the first module of its type to provide the multipurpose-testing capabilities that benchtop-WiFi-test systems require. The W-Series software now provides enhanced support for voice over WiFi, including voice-quality measurements to ensure clear and repeatable voice transmissions and a full software-test suite for comprehensive WiFiphone analysis. "By adding the voice-over-WiFi tests, Azimuth has become the first-and, currently, the only-company to offer fully automated testing of WiFi phones' roaming parameters," says Ray Cronin, the company's chief executive officer.

In addition, the company has added programmable extensions to its testMAC (mediaaccess-control) layer. These extensions permit packet-bypacket traffic generation and analysis, allowing vendors to stress-test their client-to-access-point communication. "In

**DILBERT** By Scott Adams

the past, system faults could disable an access point and compromise an entire wireless network," says Cronin. "With this addition, the testMAC can isolate problems, analyze their origins, and allow engineers to correct any anomalies."

The company now also offers a suite of scripts that implement the WiFi Alliance's (www.wi-

fi.org) interoperability tests for precertification testing. The battery of tests assures vendors that their products meet the Alliance's standards. Prices for the desktop-engineering system range from \$40,000 to \$50,000. Software licenses for the voice-over-WiFi- and WiFicertification enhancements cost \$4500 to \$9000.

-by Dan Strassberg >Azimuth Systems, www. azimuthsystems.com.

The W-Series modular desktop WiFi-test system is the first to offer fully automated testing of WiFi phones' roaming parameters.

#### - FEEDBACK LOOP

"I theorize that overly high prices encourage pirating. Send a message to the manufacturers and vendors by not buying their products."

Joseph Travis, in EDN's Feedback Loop at www.edn.com/ article/CA633438. Add your comments.

#### Line terminator says "hasta la vista" to reflections Squeezing an array of

Schottky diodes into a single package, the QDN001/ 002/003 series of diodeprotection networks from TT Electronics IRC provides line termination and ESD protection. According to Debasis Roy, PhD, director of IRC's Advanced Film Division Thin Film Business Unit, the devices require no impedance matching, because they terminate load impedances and clamp high- and low-state reflections and noise. The terminators target use with highspeed data lines, especially PCI and SDRAM buses, and reduce overshoot and undershoot with near-zero power dissipation.

The QDN001 includes 36 diodes featuring clamping current of ±50 mA, operating voltage of -0.3 to +7V, and diode forwardvoltage drop of 0.5V at 10 mA to 0.8V at 50 mA. The QDN002 series incorporates 17 diodes for ESD protection, with a 15-kV human-body-model rating and 8-kV ESD contact protection; the QDN003 has 18 Schottky diodes and similar ratings.-by Bill Schweber TT Electronics IRC.

www.irctt.com.

The QDN00x series of terminators clamps highspeed reflections, undershoots, and overshoots and protects against ESD.

## PC/104 Embedded Machine to Machine Connectivity

Keep in touch with your industrial application by using WinSystems' wired and wireless modular PC/104 modules. Small, rugged, and operational over extended temperature ranges, they are perfect for transportation, pipeline, instrumentation, MIL/COTS, and homeland security applications.

- ► Wireless

- GSM/CDMA Cellular

- 802.11 a/b/g Networking

- ► Ethernet

- 10/100 Mbps Ethernet

- Gigabit Ethernet

- ► Modem (POTS)

- ▶ USB 2.0

- ▶ RS-232/422/485 Serial I/O

- ▶ Other I/O Expansion

- A/D, D/Â

- Digital

- GPS

- ▶ Embedded Platforms Supported

- PC/104 3.6 x 3.8 inches

- EPIC 4.5 x 6.5 inches

- STD Bus 4.5 x 6.5 inches

- EBX 5.75 x 8.00 inches

- ► O/S Support

- Windows® XPe and CE

- Linux 2.6

- x86-compatible RTOS

- Extended Temperature Operation

Off-the-shelf delivery, knowledgeable technical support, and long-term availability makes these products the right choice for your application.

Call 817-274-7553 or Visit www.winsystems.com Ask about our 30-day product evaluation!

715 Stadium Drive • Arlington, Texas 76011 Phone 817-274-7553 • FAX 817-548-1358 E-mail: info@winsystems.com

## pulse

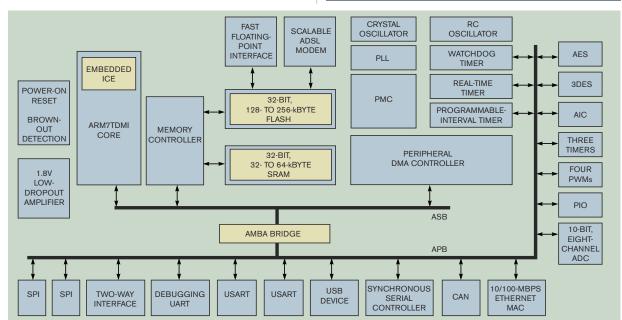

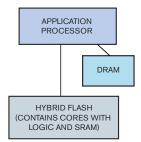

### Processor integrates more peripheral support

tmel's AT91SAM7X128 and AT91SAM7X256 ARM7-based, flash microcontrollers include peripheral support for 10/100 Ethernet; CANs (controllerarea networks); full-speed, 12-Mbps USB 2.0 devices; and high-speed AES/3DES (Advanced Encryption Standard/ Triple Data Encryption Standard) encryption in a single device. The 50-MIPS microcontrollers offer either 32 or 64 kbytes of SRAM, along with 128 or 256 kbytes of 25-nsec flash memory that supports deterministic memory access. A peripheral DMA controller connects each peripheral directly to on-chip memory, enabling high-throughput data transfers without any processor overhead. Additional peripherals include a 10-bit ADC, an eight-level priority-interrupt controller, an SPI, an SSC (synchronous serial controller), a TWI (two-way interface), UARTs, and supervisory functions. The embedded encryption engine, with the peripheral DMA controller, can encrypt or decrypt data at a rate of 80 Mbps for AES, 32.8 Mbps for DES, and 20 Mbps for 3DES.

Software-development support includes compilers, linkers, and debuggers from IAR Systems (www.iar.com), Green Hills Software (www.ghs.com), and Keil Software (www.keil.com). CMX Systems (www.cmx.com), Micrium (www.micrium.com), and FreeRTOS (www.freertos. com) offer RTOSs for the SAM7X processors. TCP/IP stacks that are available now include open-source uIP/lwIP. Micrium's royalty-free µC/ TCP-IP, and CMX Systems' royalty-free MicroNet. The AT-91SAM7X128 is available now in a green, 100-lead LQFP for \$7.20 (10,000); the AT91-SAM7X256 is available in a green, 100-lead LQFP for \$8.65 (10,000). The AT91-SAM7X-EK evaluation kit is available from Atmel for \$250.-by Robert Cravotta >Atmel, www.atmel.com.

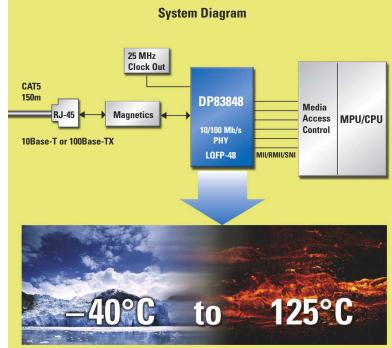

## EPIC computer pushes temperature extremes

With potential application in medical devices, security equipment, industrial machinery, aerospace projects, and transportation systems, VersaLogic's latest EPIC (embedded-platform-for-industrial-computing)-format single-board computer operates at -40 to  $+85^{\circ}$ C. The company based the Gecko design on the newer AMD GX-500 processor, which offers 500-MHz-equivalent performance and draws only about 1.5W. The low power consumption results in minimal heat dissipation, eliminating the use of an onboard fan.

The module features as much as 512 Mbytes of DDR RAM, integrated video with analog and LVDS flat-panel outputs, a stereo-I/O line, 10/100-Mbps Ethernet, analog and digital I/O, four USB ports, four communications ports, LPT and IDE (integrated-development-environment) interfaces, and a CompactFlash socket. The PC/104-Plus site accommodates both PC/104 and PC/104-Plus modules for system expansion. The Gecko includes safety features, such as transient-voltage-sup-

The new Gecko single-board computer in the EPIC form factor fits space-constrained applications with restricted cooling.

pression devices for ESD protection, self-resetting fuses for user I/O, and a watchdog timer for hardware-level application control. Prices start at \$673 (OEM quantities).

-by Warren Webb VersaLogic Corp, www.versalogic.com.

The AT91SAM7X provides an extended peripheral set that supports the ARM7 processor core.

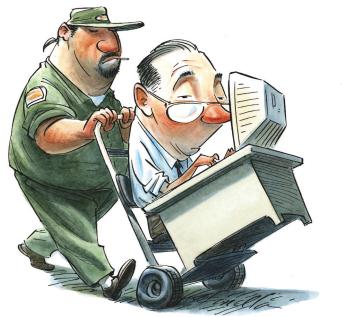

## QUESTA GIVES YOU THE POWER OF INTEGRATED VERIFICATION AND PUTS YOU IN CONTROL

You could get carried away with the confidence our verification solution inspires, but try not to let it go to your head. Mentor Graphics® Questa platform is the industry's standards-based, single-kernel verification solution that integrates HDL simulation, assertion-based verification, testbench automation, coverage-driven verification and transaction level-modeling. Questa's unparalleled language support, including SystemVerilog, is critical for the advanced verification of today's most complex designs. But remember, just because you can now tackle a faster way to reach critical verification closure than other methods, it doesn't mean you're invincible. Raise your verification confidence to new levels. Visit our website at www.mentor.com/products/fv or call 800.547.3000.

DESIGN FOR MANUFACTURING + INTEGRATED SYSTEM DESIGN ELECTRONIC SYSTEM LEVEL DESIGN + FUNCTIONAL VERIFICATION

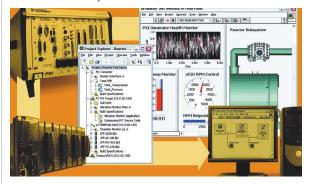

### Package provides IDE for heterogeneous distributed systems

ccording to John Pasquarette, National Instruments' director of software marketing, LabView 8, the latest release of Lab-View, is the most extensive revision yet. NI developers have been working since 1998 on some of the new features. The company's goal for the product is to provide an IDE (integrated development environment) for heterogeneous distributed systems for design, design verification, test, automation, and control. Such systems can take many forms, some of which incorporate subsystems of multiple types, including conventional PCs; intelligent modular instruments, such as PXI (PCI extensions for instrumentation); distributed I/O, such as NI's Compact FieldPoint and Compact RIO (reconfigurable I/O); PDAs; and custom-designed system components based on FPGAs. Like earlier versions of LabView, this release supports hardware from a broad spectrum of manufacturers, including NI's competitors.

To bring the many disparate elements under the LabView umbrella, the new release focuses on its ability to measure within minutes after installation, thanks to newly enhanced LabView Express features; streamlining application and device management by means of the LabView Project software module; and designing, distributing, and synchronizing intelligent devices and systems. At the heart of these functions are features either that are new to this release or

that constitute major improvements over their counterparts in earlier releases.

LabView 8 includes extensive capabilities for locating hardware and software resources that you may want to incorporate into an application. Examples are networked instruments and driver-software modules that reside on networked computers. Lab-View Project searches the network for these modules. allows you to select them for use in your project, and tracks the availability of resources that you share with another developer or project. Whereas the term "LabView Project" may make you think of the Microsoft Project (www. microsoft.com) project-management tool, the two have little in common. Although it can show you whether another developer is modifying a software module that you wish to use, LabView Project provides no configuration-control functions. It does, however, work with most popular configuration-control packages.

NI offers LabView 8 in a low-cost student version; prices for base, full, and professional versions start at \$995. Add-on components include a PDA module, which costs \$995, and FPGA, realtime, and data-logging/supervisory-control modules, each of which costs \$1995.

-by Dan Strassberg ▶National Instruments, www.ni.com/labview, ftp:// ftp.ni.com/pub/newsimages/ Constellation/LabView\_8\_% 20Distributed\_White\_Paper. pdf.

LabView 8 includes LabView Project, whose Explorer window (center left) displays the status of hardware and software resources that your project can use.

#### FEEDBACK LOOP

#### "That's what makes Design Ideas so useful; they are starting points for a design or useful concept that can be molded into an individual solution for a particular design."

Steve Hageman, in *EDN's* Feedback Loop at www.edn.com/ article/CA379888. Add your comments.

#### SMT plasma arrester features low, stable capacitance

A trio of Greentube gasplasma arresters (similar to gas-discharge tubes) from Littelfuse targets use as surge protection for broadband circuits. The devices have maximum capacitance of just 1.5 pF, along with low insertion loss, and these values remain constant over a range of voltages and temperatures, a critical factor for gigahertz-range applications.

The SL0902 devices. with a  $5 \times 5$ -mm footprint, are available in 90, 230, and 350V versions. The protectors generally work in conjunction with a fuse to provide both surge and fusing protection in applications such as telephonecompany and DSL lines, satellite boxes, and CATV interfaces. Their impulse discharge-current rating, per industry-standard test conditions, shows that they can divert a 2.5-kA pulse without destruction.

The 90V version has a dc break-over rating of 72 to 108V at 2 kV/sec with a maximum break-over voltage of 400V at 100V/  $\mu$ sec and 600V at 1 kV/  $\mu$ sec. The 230 and 350V units have dc break-over ratings of 184 to 276V and 400 to 500V, respectively; maximum break-over voltages differ somewhat. All models have an ac discharge current of 2.5A. The SL0902 devices sell for less than 20 cents (OEM quantities).

-by Bill Schweber Littelfuse Inc, www. littelfuse.com. 2 3 4 5 6 7 8 9 10

-

#### There's a Samsung MCP to fit every mobile device

Multi-Chip Packages from Samsung give your handheld designs all the memory they need in the smallest footprint. And they don't consume much power, either. Samsung MCPs stack up to eight layers of Flash, DRAM and SRAM in a myriad of configurations and densities in standard packages.

#### www.samsungusa.com/semi/mcp

© 2005. Samsung is a trademark of Samsung Electronics Company, Ltd. All other trademarks are the property of their respective owners.

BY BILL SCHWEBER

## Coating may dispel condensation fog

Researchers at the Massachusetts Institute of Technology have developed a coating, made from layers of silica nanoparticles and a special polymer, which may counter droplet accumulation on windows, goggles, and lenses. Normally, condensed droplets scatter light in random patterns, which makes the material

translucent and foggy. The coating is superhydrophilic (water-loving) and attracts the water droplets; in turn, the droplets flatten and merge into a uniform, transparent film or sheet on top of the underlying surface.

The photo shows how researchers coated one glass

slide (left) with antifogging coating and left the other one uncoated (right). They then placed the glass slides in a freezer, brought them out into humid air, and positioned them over a photo. To learn more, go to http://web.mit.edu/newsoffice/ 2005/fog.html.

>Massachusetts Institute of Technology, www.mit.edu.

## Microstrip line uses layered dielectrics for front-side antenna patch

By using multiple layers of dielectric material on a pc board, engineers at NASA's Jet Propulsion Laboratory have developed a microstrip-line patch antenna that mounts on the front of a pc board and is easy to electrically couple to the electronics. The thin, inexpensive design uses a ground plane on the underside of the high-permittivity pc-board substrate and a low-permittivitydielectric spacer layer on the top side; the microstrip patch radiator caps all sides.

Designers can use the pcboard area under the ground plane for conventional circuitry. Because there is no feed circuitry behind the ground plane, the patch antenna needs no through hole in the ground plane, minimizing RF leakage. For more, go to the September 2005 issue of *Tech Briefs* at www.techbriefs. com

#### ▷National Aeronautics and Space Administration Jet Propulsion Laboratory,

www.jpl.nasa.gov.

WIRE

CONNECTION

FROM FEED LINE

TO PATCH

HIGH-

PERMITTIVITY

DIELECTRIC

PC-BOARD

SUBSTRATE

MICROSTRIP

PATCH

RADIATOR

SIDE VIEW

For satellite and cellular base stations, a GaN (gallium-nitride) power FET from Toshiba Corp surpasses the output of GaAs (gallium-arsenide) devices, improving power

density by a factor of eight. Currently available GaAs devices are rated at about 90W/6 GHz and 30W/14 GHz, but GaN has higher saturation electron velocity, dielectric breakdown voltage, and operating-temperature range than GaAs. These factors are important for achieving higher power gigahertz-range operation.

The device uses an epitaxial-layer structure, with optimized FET layout and dimensioning, plus a new surface-treatment process for low contact resistance and low gate-leakage current. Toshiba's production also requires a modified version of the conventional stepper process, which is better for mass-production than the electron-beam lithography process that C-band GaN devices commonly use. A GaN power-FET chip measures 2.92×0.71 mm, and the outer cavity of a packaged device with four chips, such as the one in the photo, measures 24.5×17.4 mm. For more, go to www.toshiba.co.jp/about/press/2005\_09/pr1201.htm. Toshiba Corp, www.toshiba.co.jp.

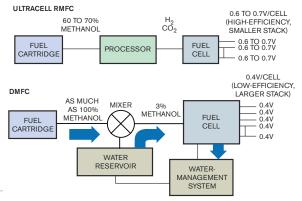

#### Fuel cell beats power-density benchmarks

UltraCell Corp claims that its cells, using a reformed-methanol technology, provide significantly more power density than the conventional "direct-methanol" approach and twice the power density of lithium batteries. Key to the improvement is a microreformer, which the company says generates fuel-cell-ready hydrogen from a highly concentrated methanol solution. The approach requires no water reservoir, cleanup, distinct internal reformer, or water-management system. UltraCell has shipped 32-oz prototypes to the military. Those devices deliver 45W continuous power and 20W average output over 24 hours. For more, got to www.ultracellpower.com.

MICROSTRIP

TRANSMISSION

(FEED LINE)

GROUND PLANE

LOW-

PERMITTIVITY

DIELECTRIC

SPACER

LAYER

#### UNLEASH BROADBAND WITH FUJITSU'S WIMAX 802.16-2004 SoC.

With a MAC-to-PHY implementation based on the IEEE 802.16-2004 broadband wireless access standard, the Fujitsu WiMAX SoC, MB87M3400, offers a cost-effective solution for both subscriber station and base station applications. This highly integrated SoC implements MAC, PHY, radio control and all the necessary analog circuits for the appropriate 2 to 11GHz licensed or license-exempt bands. The Fujitsu WiMAX SoC fully complies with the IEEE 802.16-2004 standard using an OFDM PHY.

#### **ADVANCED FEATURES**

- 256 OFDM PHY with 64QAM, 16QAM, QPSK and BPSK modulation

- Uplink subchannelization

- Flexible baseband interface with integrated high-performance ADC and DAC

- Security implementation using DES, CCM encryption/decryption

- Rich set of integrated peripheral and RF control

For more information, call (800) 866-8608 or visit http://us.fujitsu.com/micro/wimax

THE POSSIBILITIES ARE INFINITE

##

#### **GLOBAL DESIGNER**

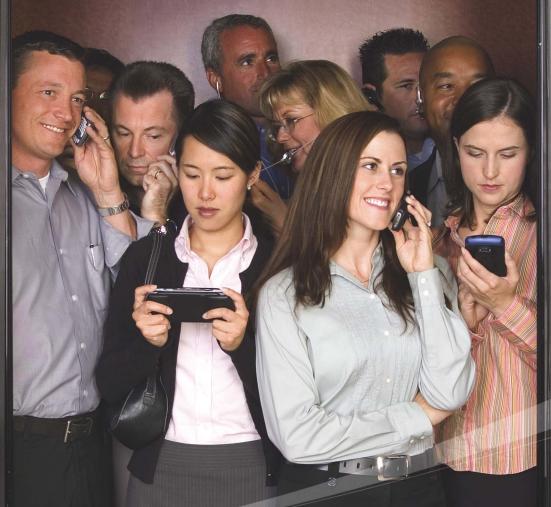

## Low-cost handsets gain traction in India

urgeoning demand from mobile-service operators for ultralowcost handsets to service pricesensitive emerging markets, such as India, is motivating semiconductor vendors to develop single-chip-handset offerings. For example, Texas Instruments recently demonstrated the first less-than-\$40 handsets built in India from concept to design to production. BPL Ltd (www.bplmobile. com) and Quasar Innovations (www.quasarinnovations.com) based the Primus GSM phones that they developed on TI's TCS chip set. These handsets incorporate only basic voice and short-message service-no cameras, color screens, or MP3 players, instead emphasizing low cost and an intuitive user interface.

"We expect the industry will be selling an ultralow-cost mobile phone for less than \$20 by the start of 2006. These costs include electronic components, connectors, the pc board, the casing with display and keypad, software, and the battery," says Horst Patch, vice president of the Communication Business Group at Infineon Technologies.

Ultralow-cost handsets will enable telephony in parts of the world in which land-line service is unavailable or unreliable, says Douglas Grant, business-development manager with Analog Devices' RF and Wireless Systems Group. Grant adds that chip-set suppliers pursuing the ultralow-cost-handset market need to provide robust reference platforms and even complete turnkey designs with preloaded software features to simplify the development of the final handset product.

"In phone design, there are a few major building blocks among them: digital baseband, analog baseband, RF section, and memory, which comprise the bulk of the cost drivers for these handsets," explains Harish M, general manager of business development at TI India. An ultralow-cost handset should have no more than 100 components, compared with 600 or more for a high-end feature phone or smart phone.

Grant says that manufacturers can reduce BOM (bill-ofmaterials) costs by integrating core handset functions, such as digital and analog processing, power management, and a radio transceiver, into one chip. But this approach is risky, because it requires a high-performance wafer process, and may be unsuited for consistent production. Infineon's new, low-cost E-Goldradio handset combines the baseband processor and the RF transceiver in a  $9 \times 9$ mm-footprint chip.

"A lower risk approach is to combine functions into a system-in-package design, which saves board area and manufacturing cost but retains the performance of the radio and minimizes risk because vendors can easily port software to such a device," says Grant.

Infineon's new, low-cost E-Goldradio handset combines the baseband processor and the RF transceiver in a 9×9mm-footprint chip. It enables manufacturers to implement the baseband and RF functions on less than 4  $\mbox{cm}^2$  of board space-about 30% less than two-chip offerings require. It also cuts the BOM cost by about 30% by eliminating external components, including capacitors and discrete components, that a two-chip approach requires. And a lowcomponent-count design and simplified layout enable the use of cheap, four-layer pc-

board technology and singleside mounting, further reducing manufacturing costs. TI also offers the similar single-chip DRP (digital-radio processor).

-by Chitra Giridhar, EDN Asia

► Analog Devices, www. analog.com.

**Infineon**, www.infineon. com.

**Texas Instruments**, www. ti.com.

#### Japanese-automotive software goes horizontal

Toyota Motors is moving to a horizontal and cooperative model for software development to meet the increasing demand for more sophisticated and widespread automotive electronics. Traditionally, Japanese designers in the automotive industry have developed software for single applications instead of using standardized software platforms upon which vendors could build myriad applications, according to Koichi Tanigawa, general manager of the development department at the integrated-system-engineering division of the vehicleengineering group of Toyota. He recently spoke at the Freescale (www.freescale.com) Technology Forum Japan 2005 in Tokyo.

With the increased use of microcontrollers and sensors in such automotive applications as vehicle control, safety, and pollution control, automotive electronics have become hot markets. Fulfilling the needs of those applications requires a lot more software development, he says.

In the Japanese-automotive industry, suppliers and automotive manufacturers have a vertical-integration relationship, in which conventional and limited suppliers deliver components to automotive manufacturers. This approach makes suppliers a type of subsidiary of the automakers in vertical-integration systems. For example, Toyota has developed its own dedicated software. But, as the amount of the software increases, it is using multiple developers to develop individual layers, including the operating system, middleware, and applications.—**by Takatsuna Mamoto**, *EDN Japan*

Toyota Motor Corp, www.toyota.com/jp.

10.13.05

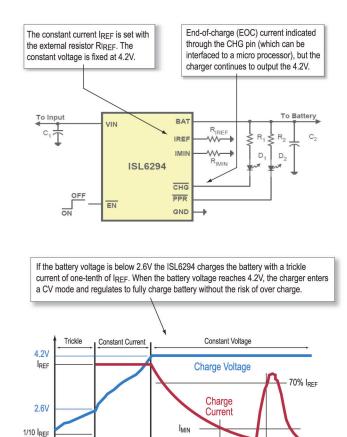

### **Intersil Battery Charger ICs**

Intersil High Performance Analog

## Have **YOU** Seen the World's Smallest Battery Charger IC?

Not only is the 2mm x 3mm ISL6294 the industry's smallest, but this fully integrated, single-cell Li-Ion / Li-Polymer battery charger IC can handle input voltages up to 28V, eliminating the need for an over-voltage protection circuit.

#### Key Features:

- 2mm x 3mm 8 Ld DFN package

- 28V maximum input voltage

- Programmable end-of-charge current with status interfaced to a micro device through CHG pin

- Thermaguard<sup>™</sup> charge current thermal foldback for thermal protection

- No external blocking diode required

- Integrated pass element and current sensor

- 1% voltage accuracy

- Trickle charge for fully discharged batteries

- Less than 1µA leakage current off the battery when no input power attached or charger disabled

- Input over-voltage protection

- End-of-charge indication with large hysteresis to prevent unwanted re-charge

Datasheet, free samples, and more information available at www.intersil.com/edn

HIGH PERFORMANCE ANAL OG

Time

Intersil – Switching Regulators for precise power delivery.

CHG

Indication

©2005 Intersil Americas Inc. All rights reserved. The following are trademarks or services marks owned by Intersil Corporation or one of its subsidiaries, and may be registered in the USA and/or other countries: Intersil (and design) and i (and design).

**TYPICAL CHARGE PROFILE**

CHG

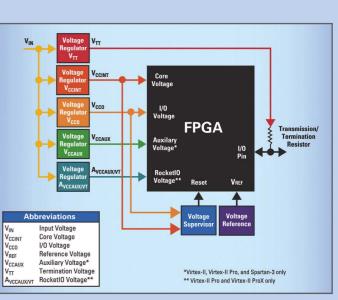

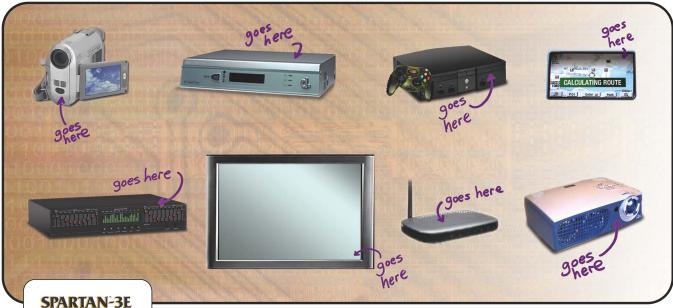

## **Power Management** for FPGAs

**High Performance Analog Solutions**

Power management and signal chains demand a system approach that's why Avnet Electronics Marketing and National Semiconductor together are such a powerful combination.

- Power and signal chain products that blend maximum performance with overall efficiency

- Collaborative engineering support from conceptual design through volume manufacturing

- System level expertise to assist in determining the right architecture and products for your application

- Factory-trained Field Application Engineers well versed in National's technology and tools

- Broad portfolio of devices to compliment FPGA-based designs

- Solutions sample kits to assist you in your designs

Whether you're working on a portable, handheld, security, medical or other analog design, let Avnet EM help you solve your power and signal design challenges and get your application up and running.

For sample kits, web seminars and design tools, go to avnet.national.com

### **FPGAs in High Performance Systems**

FPGAs enable developers to accelerate high performance applications by integrating I/O acquisition and processing functions into programmable logic. While system power is primarily determined by how logic is utilized and how fast it is clocked, the selection of power components has a substantial impact on the efficiency of power supply systems and, as a consequence, on overall power consumption.

#### To read this case study. go to avnet.national.com

#### POWER MANAGEMENT DESIGN **GUIDE FOR XILINX® FPGAS**

The National Power Management Design Guide features parametric tables, sample designs and step-by-step directions, making it a fast, accurate source for choosing the best National power supply solutions for your Xilinx FPGA-based applications.

#### The recommended power supply solutions feature voltage regulators, voltage supervisors and voltage references.

The guide also details available design tools, including the National Dual High-Current Power Supply Kit developed by Avnet (part # ADS-NSC-XP).

Learn more at avnet.national.com

S

All rights reserved

2005.

Enabling success from the center of technology™

1 800 332 8638

#### **Reigning in Power Consumption** for FPGA-Based Applications

Through an understanding of the interdependencies of power systems, developers can include power considerations in the early stages of design that will simplify power supply design and maximize the power efficiency of the final architecture. Industry expert Nicholas Cravotta explores the key issues behind managing power in FPGA-based high performance systems, including:

- How to efficiently and cost-effectively supply all of the different voltages an FPGA requires